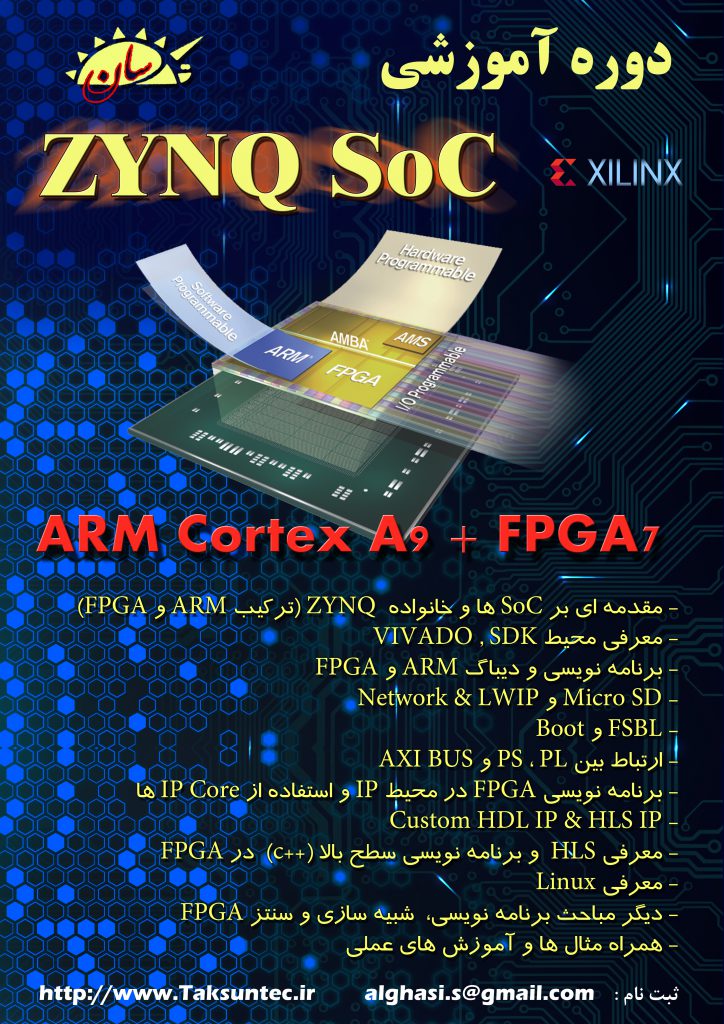

دوره آموزشی ZYNQ SoC FPGA در VIVADO

<<برای مطالعه مقالات آموزشی رایگان مرتبط با FPGA به بخش مقالات مراجعه نمایید>>

تکسان مفتخر است اولین برگزار کننده رسمی دورهای برنامه نویسی نوین FPGA در کشور است. این دوره ها شامل ZYNQ SoC و HLS می باشد که از سال ۱۳۹۴ به صورت عمومی برگزار می گردد.

از سال ۱۳۹۵ دوره آموزش عملی ZYNQ با همکاری دانشگاه علم و صنعت در این دانشگاه برگزار شده است. برای یادگیری بهتر، این دوره به صورت پروژه محور و کار عملی بر روی برد برگزار می شود. در این دوره علاوه بر سرفصل های اصلی ZYNQ، مطالب جانبی دیگری در خلال کار عملی با ZYNQ آموزش داده می شود که شامل کار با VIVADO، کار با ILA یا همان چیپ اسکوپ، اساس کار با باس های AXI و HLS و … میباشد.

به منظور افزایش حداکثری کاربردی بودن کلاس های آموزشی، همکاری با شرکت آرتمیش کاریا را آغاز نموده ایم. هنرجویان برتر بعد از گذراندن کلاس های آموزشی توسط این مرکز در صنعت های مختلف کشور جذب می شوند تا بتوانند در پیشرفت صنعت کشور سهیم باشند.

دوره ها هم به صورت حضوری هم به صورت برخط برگزار میگردد.

نکات:

- تمرکز این دوره بر استفاده از امکانات ZYNQ ، استفاده از IP Core ها و برنامه نویسی در Block Design است.

- مثال های عملی با برد های شرکت آرتمیس کاریا انجام می شود ولی مطالب و پروژه ها با تمامی برد های ZYNQ سازگار هستند.

پیش نیاز:

- آشنایی مقدماتی با FPGA و یکی از زبانهای HDL

- آشنایی مقدماتی با یکی از میکرو کنترلرها با زبان C

هزینه دوره : ۵،۶۰۰،۰۰۰ تومان

ثبت نام :

دوره آموزش عملی ZYNQ در VIVADO

سرفصل های آموزشی:۶

آشنایی با SoC و معرفی ZYNQ

- مقدمه ای بر SoC و تاریخچه آن ها

- معرفی انواع پردازش و پلتفرم های پردازشی

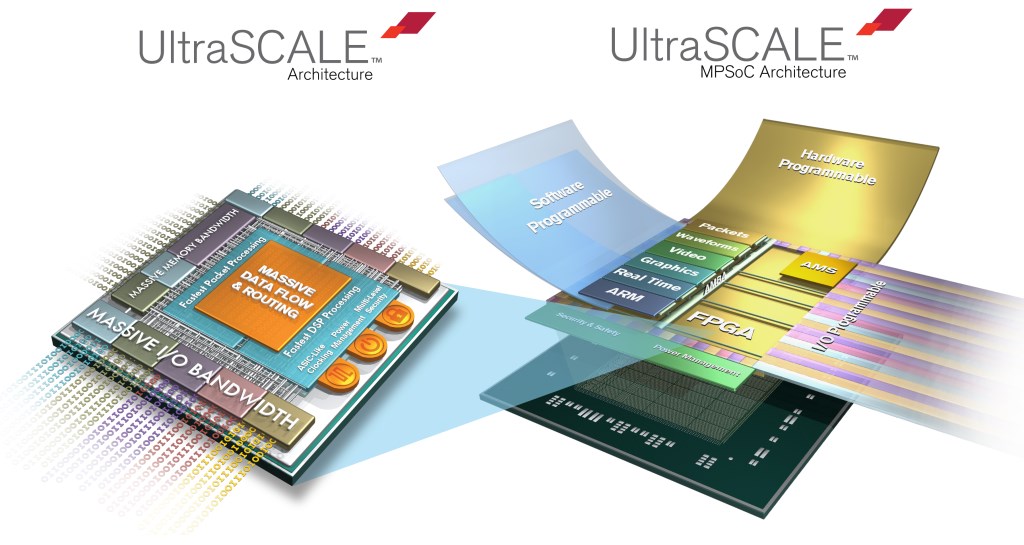

- معرفی ZYNQ و انواع آن

- معرفی ساختار داخلی ZYNQ 7000

- بررسی نقاط قوت و نقاط ضعف

معرفی محیط VIVADO

- معرفی بخش های مختلف VIVADO

- مقایسه با ISE

- معرفی روش کار کرد به صورت HDL و به سبک ISE

- معرفی محیط Block Design و استفاده گرافیکی از IP core ها

معرفی محیط SDK

- معرفی محیط SDK برای برنامه نویسی پردازنده ARM و Micro Blaze

- کامپایل و ساخت پروژه به صورت Bare-metal

- پروگرام کردن FPGA و ARM

- دیباگ برنامه های ARM

- ساخت Boot

پروگرام و دیباگ

- پروگرام کردن ARM

- پروگرام کردن FPGA

- دیباگ برنامه های ARM در SDK

- مراحل مختلف Boot و انواع Boot

- بوت از طریق uSD و QSPI

- برنامه FSBL

کار با Peripheral ها و ابزار های جانبی

- کار با UART

- کار با GPIO های ARM

- کار با EMIO و ارتباط ساده PS و PL

- کار با AXI GPIO و ارتباط AXI با PL

- کار با IO های FPGA

- کار با شبکه ۱G

- کار با حافظه micro SD

- معرفی کتابخانه ها و داکیومت ها برای استفاده از Peripheral های دیگر

کتابخانه های Middleware برای شبکه و FAT

- کار با کتابخانه ff و Micro SD

- ساخت فایل باینری و TEXT و خواندن از فایل ها

- کار با شبکه ۱G و کتابخانه LWIP

- ارسال داده UDP/IP

- ارسال داده TCP/IP و مثال telnet

- حل مشکلات برد Z-TURN

تنظیمات PS، معرفی TCL و Definition Board

- کار با IP Core مخصوص PS چیپ ZYNQ

- ذخیره تنظیمات و بازیابی با TCL

- استفاده از Definition Board و کار با برد های معروف

- ارائهDefinition Board برای Z-TURN

AXI BUS

- معرفی باس محبوب AXI

- انواع باس AXI

- معرفی سیگنال ها

- کار با AXI – LITE

- مشاهده سیگنال ها در لاجیک آنالایزر

- کار با AXI در VHDL

معرفی ILA و چیپ اسکوپ

- معرفی Integrate Lagic Analaize یا چیپ اسکوپ

- استفاده از ILA در Block Design

- مشاهده سیگنال های AXI-LITE در VIVADO

نوشتن کد HDL و ساخت IP Core دلخواه

- نوشتن کد های VHDL و Verilog و ترکیب با Block Design

- نوشتن IP Core دلخواه با HDL

- نوشتن یک IP Core ساده با AXI -LITE با VHDL و اتصال آن به PS چیپ ZYNQ

ارتباط PS و PL

- معرفی گذرگاه های بین PL و PS

- کار با Master GP

- انجام پروژه اشتراک گذاری Block RAM بین ps و pl

معرفی HLS و برنامه نویسی C++ برای FPGA

- معرفی HLS

- معرفی محیط نرم افزار HLS

- معرفی نحوه برنامه نویسی و کلیات HLS

- شبیه سازی در HLS

- ساخت یک بلوک پردازشی با Cpp ساده و استفاده از AXI-LITE و اتصال آن به PS چیپ زینک

گذرگاه AXI HP و DMA

- کار با درگاه AXI HP

- AXI DMA

- انتقال داده حجیم و سرعت بالا بین PS و PL

معرفی لینوکس روی ZYNQ

- معرفی لینوکس

- انواع لینوکس روی ZYNQ

- معرفی اجمالی نحوه کامپایل لینوکس روی ZYNQ