فروردین

Micro FPGA ها و Embedded FPGA ها

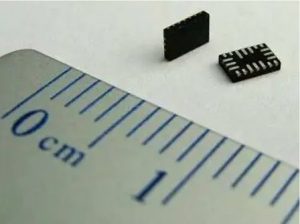

وقتی برنامه نویسان اسم FPGA به گوششان می خورد, همه با خود به فکر پر مصرف بودن, بزرگ بودن و گران بودن این تکنولوژی می افتند. Renesas خانواده Forge FPGA خود را معرفی کرده است. که یک (eFPGA (embedded FPGA است. جزئیات در وبسایت Renesas قرار دارند. Forge FPGA ها که بسیار کوچک هستند و جریان مصرفی آن ها در محدوده ی میکرو آمپر است نشان می دهند که FPGA ها لازم نیست که بزرگ, پر مصرف و گران باشند. همچنین انتظار می رود که Forge FPGA ها به صورت عمده و به قیمت زیر ۵۰ سنت به بازار عرضه شوند.

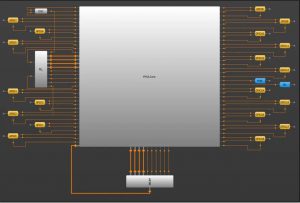

Forge FPGA ها به همراه یک بسته ی نرم افزاری کامل عرضه می شوند که قابلیت برنامه نویسی با Verilog یا رابط گرافیکی IP block wizard دارد. در رابط گرافیکی می توان یک بلوک منطقی را بدون هیچ گونه کد نویسی Verilog پیاده سازی کرد.همچنین بسته ی نرم افزاری دارای یک شبیه ساز هم هست. راهنمای کاربر Forge FPGA به صورت آنلاین در دسترس است. در اینجا نمای top level یک بلوک منطقی در رابط گرافیکی Forge FPGA آمده است:

هسته این FPGA آرایه ای از بلوک های EFLX eFPGA است که مستقیماً به GPIO، BRAM، PLL و غیره متصل می شود. در زیر یک اسکرین شات از نتایج P&R آمده است:

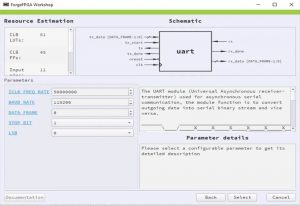

در نهایت، در شکل زیر, نمونه ای از یک IP Block در رابط کاربری آورده شده است:

بلوک EFLX 1K eFPGA برای طرح های SoC

Renesas به ما نشان می دهد که FPGA لازم نیست بزرگ و پر مصرف باشد. Renesas از بلوک های EFLX 1K eFPGA در Forge FPGA استفاده می کند، و می توان در SoC خود برای انجام عملکردهای “Glue Logic” مانند GPIO به کار گرفت. همچنین در بخش هایی از SoC که بایستی با تغییرات غیرقابل پیش بینی در نیازهای مشتری و یا با پروتکل ها و الگوریتم ها مختلف سازگار کرد، می توان به کار گرفت. در حال حاضر بلوک EFLX 1K در دسترس است و توسط TSMC 40ULP توسعه داده شده است. یک تراشه به اندازه ی حدود ۱٫۵ میلی متر مربع فضا می گیرد که آن مقدار در TSMC N7 به ۰٫۲ میلی متر مربع کاهش پیدا می کند. با چنین eFPGA کوچکی می توان مانند هسته های کوچک ARM, آن ها را در اطراف SoC پخش کرد. بلوک ها EFLX 1K یک FPGA مستقل با ۳۶۸ ورودی خروجی است که هر کدام دارای Flip Flop اختیاری است که می تواند به پردازنده یا گذرگاه های جانبی متصل شود و همچنین می تواند GPIO محلی را با پروتکل های مختلف کنترل کند یا می تواند یک ماشین حالت برای کنترل مسیرهای داده باشد. برای مثال یک EFLX 1K به عنوان ۱۶۴۵۰ UART یا I2C Master یا SPI Master قابل برنامه نویسی است. بلوک EFLX 1K می تواند ارایه ای از LUT های ۲K، ۴K، ۸K، ۱۶K یا بیشتر باشد. یک آرایه ۱۶K دارای ۴ برابر ورودی خروجی یک EFLX 1K خواهد بود.

بدون ديدگاه